## **ARTICLE IN PRESS**

Nuclear Instruments and Methods in Physics Research A I (IIII) III-III

Contents lists available at ScienceDirect

# Nuclear Instruments and Methods in Physics Research A

journal homepage: www.elsevier.com/locate/nima

# Developments of SOI monolithic pixel detectors

Y. Arai<sup>a,\*</sup>, T. Miyoshi<sup>a</sup>, Y. Unno<sup>a</sup>, T. Tsuboyama<sup>a</sup>, S. Terada<sup>a</sup>, Y. Ikegami<sup>a</sup>, T. Kohriki<sup>a</sup>, K. Tauchi<sup>a</sup>, Y. Ikemoto<sup>a</sup>, R. Ichimiya<sup>a</sup>, H. Ikeda<sup>b</sup>, K. Hara<sup>c</sup>, H. Miyake<sup>c</sup>, M. Kochiyama<sup>c</sup>, T. Sega<sup>c</sup>, K. Hanagaki<sup>d</sup>, M. Hirose<sup>d</sup>, T. Hatsui<sup>e</sup>, T. Kudo<sup>e</sup>, T. Hirono<sup>e</sup>, M. Yabashi<sup>e</sup>, Y. Furukawa<sup>e</sup>, G. Varner<sup>f</sup>, M. Cooney<sup>f</sup>, H. Hoedlmoser<sup>f</sup>, J. Kennedy<sup>f</sup>, H. Sahoo<sup>f</sup>, M. Battaglia<sup>g</sup>, P. Denes<sup>g</sup>, C. Vu<sup>g</sup>, D. Contarato<sup>g</sup>, P. Giubilato<sup>g</sup>, L. Glesener<sup>g</sup>, R. Yarema<sup>h</sup>, R. Lipton<sup>h</sup>, G. Deptuch<sup>h</sup>, M. Trimpl<sup>h</sup>, M. Ohno<sup>i</sup>, K. Fukuda<sup>i</sup>, H. Komatsubara<sup>i</sup>, J. Ida<sup>i</sup>, M. Okihara<sup>j</sup>, H. Hayashi<sup>j</sup>, Y. Kawai<sup>j</sup>, A. Ohtomo<sup>j</sup>

<sup>a</sup> Institute of Particle and Nuclear Studies, High Energy Accelerator Research Org., KEK, Tsukuba 305-0801, Japan

<sup>f</sup> Department of Physics and Astronomy, University of Hawaii, 2505 Correa Rd., 96822 Honolulu HI, USA

<sup>h</sup> Fermilab, Batavia, IL 60510-5011, USA

#### ARTICLE INFO

#### ABSTRACT

*Keywords:* SOI Pixel X-ray imaging Particle tracking A monolithic pixel detector with 0.2 µm silicon-on-insulator (SOI) CMOS technology has been developed. It has both a thick high-resistivity sensor layer and thin LSI circuit layer on a single chip. Integration-type and counting-type pixel detectors are fabricated and tested with light and X-rays. The process is open to many researchers through Multi Project Wafer (MPW) runs operated by KEK. Further improvements of the fabrication technologies are also under investigation by using a buried p-well and 3D integration technologies.

© 2010 Elsevier B.V. All rights reserved.

### 1. Introduction

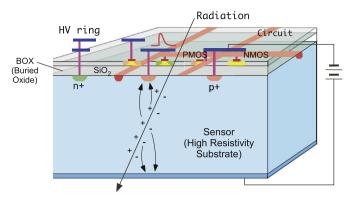

A monolithic pixel detector, in which both semiconductor sensors and readout electronics are fabricated on the same wafer has many attractive features for applications in high-energy experiments, astrophysics, material analysis, medical imaging and so on. We have realized such a detector by using a SOI (silicon-oninsulator) technology which bonds wafer of thick, high-resistivity Si and thin low-resistivity Si together (see Fig. 1)[1,2].

Some of the SOI pixel detector features are

- No mechanical bump bonding, so obstacles which will cause multiple scattering are minimized and smaller pixel size is possible.

- Parasitic capacitances of sensing nodes are very small ( $\sim 10 \, \text{fF}$ ), so large conversion gain and low noise is possible.

- Full CMOS circuitry can be implemented.

0168-9002/\$ - see front matter  $\circledcirc$  2010 Elsevier B.V. All rights reserved. doi:10.1016/j.nima.2010.02.190

- Cross-section of single event effects is very small.

- The technology is based on industry standards, so further progress and low cost is envisaged.

- SOI transistors are shown to work over a very large temperature range from 4 to 600 K.

#### 2. SOI pixel process and MPW run

We have developed a 0.2  $\mu$ m SOI pixel process in collaboration with OKI Semiconductor Co. Ltd. The basic technology for fabricating the pixel detector is OKI's fully-depleted 0.2  $\mu$ m CMOS SOI process [3]. Additional processing steps to create substrate implants and contacts between the implant nodes to the circuitry were established. Main specifications of the process are summarized in Table 1.

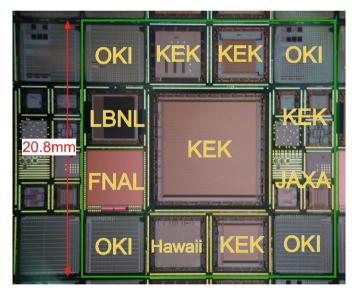

To reduce development cost of a design, we have been organizing MPW (Multi Project Wafer) runs. Two MPW runs were completed and one run is being processed now. In each run, we have about 16 designs from our collaborators [4–6]. Photograph of the last MPW run wafer is shown in Fig. 2.

<sup>&</sup>lt;sup>b</sup> Institute of Space and Astronautical Science, JAXA, Sagamihara, Kanagawa 229-8510, Japan

<sup>&</sup>lt;sup>c</sup> Institute of Pure and Applied Sciences, University of Tsukuba, Tsukuba, Ibaraki 305-8577, Japan

<sup>&</sup>lt;sup>d</sup> Osaka University, 1-1 Machikaneyama, Toyonaka, Osaka 560-0043, Japan

<sup>&</sup>lt;sup>e</sup> Riken, 1-1-1, Kouto, Sayo-cho, Sayo-gun, Hyogo 679-5148, Japan

<sup>&</sup>lt;sup>g</sup> Lawrence Berkeley National Laboratory, Berkeley, CA 94720, USA

<sup>&</sup>lt;sup>i</sup> Oki Semiconductor Co. Ltd., Higashiasakawa, Hachioji, Tokyo 193-8550, Japan

<sup>&</sup>lt;sup>j</sup> Oki Semiconductor Miyagi Co. Ltd., Ohira-mura, Kurokawa-gun, Miyagi 981-3693, Japan

<sup>\*</sup> Corresponding author. Tel.: +81298796211; fax: +81298643284. *E-mail address:* yasuo.arai@kek.jp (Y. Arai).

### **ARTICLE IN PRESS**

Y. Arai et al. / Nuclear Instruments and Methods in Physics Research A I (IIII) III-III

Fig. 1. Cross sectional view of a SOI pixel detector.

#### Table 1

SOI pixel process specification.

| Process   | 0.2 μm low-leakage fully-depleted SOI CMOS, 1 Poly, 4 metal                |

|-----------|----------------------------------------------------------------------------|

|           | layers, MIM Cap., DMOS options, Core (I/O) voltage=1.8 (3.3) V             |

| SOI wafer | Diameter: 200 mm $\phi$ , Top Si: Cz $\sim$ 18 $\Omega-$ cm, p-type, 40 nm |

|           | thick. Buried Oxide: 200 nm thick,                                         |

|           | Handle wafer: Cz $\sim$ 700 $\Omega-cm,$ n-type, 725 $\mu m$ thick         |

| Backside  | Thinned to 260 $\mu$ m, and sputtered with Al (200 nm).                    |

|           |                                                                            |

**Fig. 2.** Photograph of a Multi Project Wafer processed in 2008. In addition to Japanese laboratories and universities, there are designs from US institutions.

### 3. Pixel detectors

We are developing two kinds of pixel detectors. One is an integration-type pixel called INTPIX2, and the other is a counting-type pixel called CNTPIX2. In these detectors, reverse bias voltage is applied from the bottom surface or top n + HV ring. Breakdown voltage is observed between 50 and 230 V depending on the pixel layout. Leakage current is less than  $0.1 \text{ pA}/\mu\text{m}^2$ .

#### 3.1. Integration-type pixel

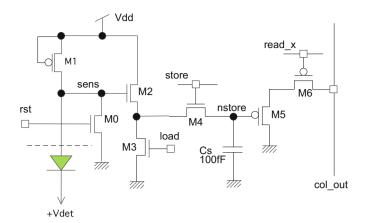

A schematic of the INTPIX2 is shown in Fig. 3. Chip size is 5 mm by 5 mm and has  $128 \times 128$  pixels each  $20 \,\mu$ m square. Fig. 4

Fig. 3. Schematic of the integration type pixel (INTPIX2).

**Fig. 4.** X-ray image taken with the integration type pixel. The results are shown for three space resolution patterns from 12.5 to 20 lp/mm.

shows a test chart image taken by the INTPIX2 with 8 keV X-rays. It indicates 20 lines/mm is well resolved. Each pixel has a window to illuminate light from topside to ease testing. It is possible to shrink the pixel size to less than  $10 \,\mu$ m square.

#### 3.2. Counting-type pixel

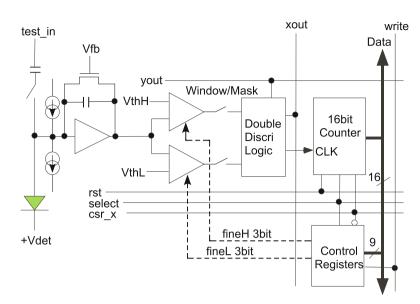

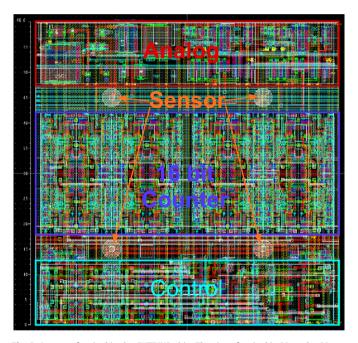

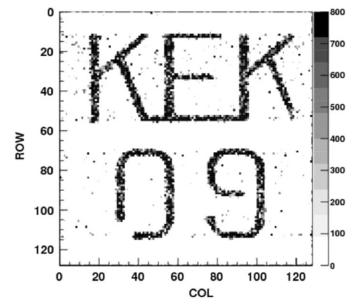

A pixel circuit of the CNTPIX2 is shown in Fig. 5. The preamplifier circuit is same type proposed by Krummenacher [7] which contains leakage current compensation circuitry. After the low and high threshold discriminator, the input signal is counted in a 16-bit counter. Layout of the CNTPIX2 is shown in Fig. 6. There are 128 x 128 pixels in a 10.2 mm square chip. A metal plate image taken with 8 keV X-ray is shown in Fig. 7 and the operation was confirmed. We also see some crosstalk within a pixel and inefficiencies, so detailed study is continuing.

#### 4. On-going R&D

Since the sensor nodes and circuits are placed very close together in the SOI pixel detector, there will be some interference between them. One of the newly developed techniques is buried p-well creation in the substrate. We implant p-type dopant through the top Si layer and create a buried p-well (BPW) region under the BOX. This BPW region will help to fix the underside

2

# ARTICLE IN PRESS

Y. Arai et al. / Nuclear Instruments and Methods in Physics Research A I (IIII) III-III

Fig. 5. Circuit of the CNTPIX2 pixel.

Fig. 6. Layout of a pixel in the CNTPIX2 chip. The size of a pixel is  $60\,\mu$ m by  $60\,\mu$ m, and each pixel contains about 600 transistors.

potential of the transistors and reduce the so called back gate effect. The doping level of the BPW is about 3 orders lower than that of the p+ sensor node and drain/source region, so it does not affect the transistor characteristics in the top Si layer. Another direction is 3D vertical integration. We will bond two SOI wafers face to face by using micro-bump technology of ZyCube Co. Ltd [8]. Minimum pitch of the bump is  $5 \,\mu$ m. This will enable higher circuit integration density and separate the sensitive circuit regions from the sensors.

#### 5. Summary

We have developed SOI based pixel technology and organized MPW runs by collecting designs from many laboratories and universities. The number of MPW runs will be increased to twice/year. We have demonstrated basic performance of the SOI

Fig. 7. X-ray Image of a metal mask taken with the CNTPIX2.

integration-type and counting-type pixel detectors. To reduce the back-gate effect and improve radiation hardness, we are trying buried p-well technology and 3D integration technology.

### Acknowledgements

The authors wish to thank F. Takasaki and J. Haba for their continuing support to this project. This work is supported by VLSI Design and Education Center (VDEC), The University of Tokyo with the collaboration of the Cadence Corporation and Mentor Graphics Corporation.

### References

- [1] SOIPIX collaboration. < http://rd.kek.jp/project/soi/>.

- [2] Y. Arai, Electronics and Sensor Study with the OKI SOI process, in: Proceedings of Topical Workshop on Electronics for Particle Physics (TWEPP-07), CERN-2007-007, pp. 57–63.

#### 4

# **ARTICLE IN PRESS**

### Y. Arai et al. / Nuclear Instruments and Methods in Physics Research A I (IIII) III-III

- [3] K. Morikawa, Y. Kajita, M. Mitarashi, OKI Technical Review, Issue 196, 70(4) (2003) 60.

- M. Battaglia, et al., Nucl. Instr. and Meth. A 583 (2007) 526.

D. Kobayashi, et al., IEEE Trans. Nucl. Sci. NS-55 (2008) 2872.

- [6] K. Hara, et al., Nucl. Sci. Symp. Conf. Record (2008) 1369.

- [6] K. Hatti, et al., reter, Soc. Synty. commeticate (1607) (1607) (17)

[7] F. Krummenacher, Nucl. Instr. and Meth. A 305 (1991) 527.

[8] M. Motoyoshi, M. Koyanagi, 3D-LSI technology for image sensor, 2009 JINST 4 P03009 doi:10.1088/1748-0221/4/03/P03009.